Animação VGA

No modo VGA a tela é dividida em pontos (pixels) que são separados por linhas e colunas. Geralmente a imagem possui 480 linhas e 600 colunas e somente um pixel é aceso de cada vez. Para formarmos uma tela, utilizamos o efeito da persistência da visão utilizado também no projeto Multiplexação de display de 6 algarismos.É extremamente recomendável que leia-se a página do Padrão de Cores VGA pois este projeto está intimamente ligado a ele.

O projeto descrito a seguir é um exemplo de circuito lógico sequencial, descrito em VHDL e simulado software ModelSim®-Altera, utilizando um testbench.

Os equipamentos necessários para a implementação do projeto são:

- 1x Kit CPLD 7064;

- 1x Monitor com porta VGA;

- 1x Placa de interface VGA;

- 1x Adaptador para matriz de contatos

Lógica de Funcionamento

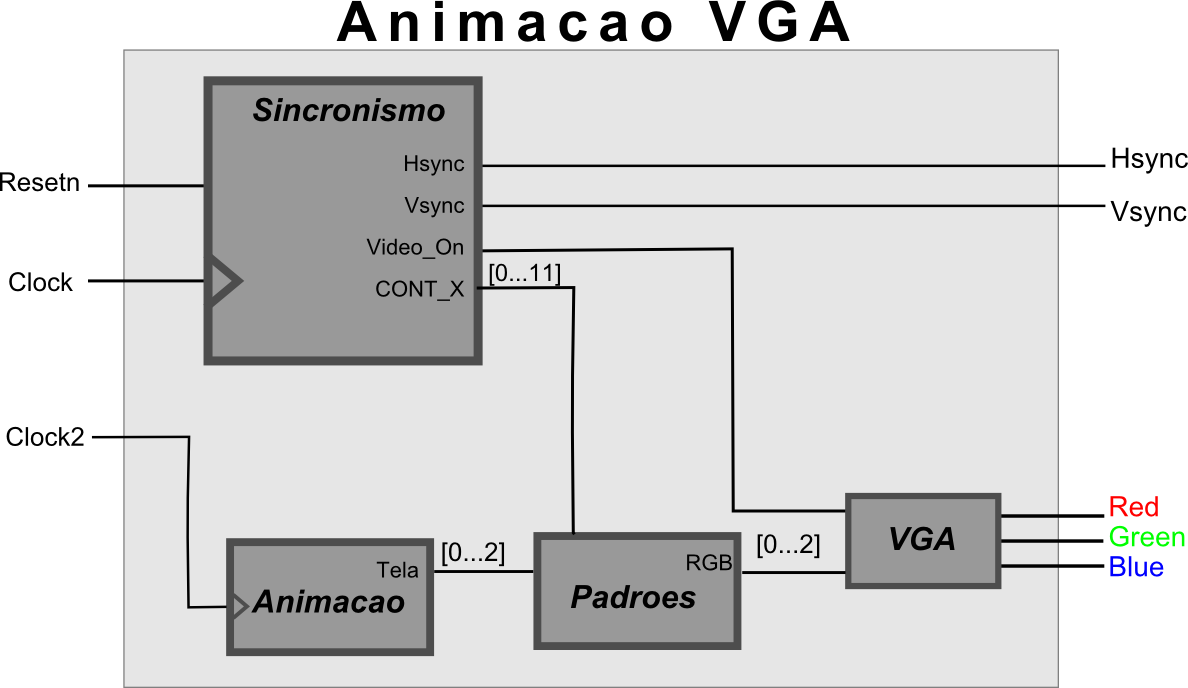

Este projeto difere do Padrão de Cores em apenas dois aspectos. Possui um contador de baixa frequência e um mutiplexador que avalia o estado da contagem.

Figura 1 – Diagrama de blocos

Animação

Um bloco conta os pulsos do clock de baixa frequência (Clock2). O valor do contador é transmitido pelo sinal Tela, que varia de 0 a 5 e é lido pelo bloco Padrões.

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 |

ANIMACAO: process(CLOCK2) begin if (CLOCK2'event) and (CLOCK2='1') then if RESET = '1' then TELA <= "000"; else if TELA = "101" then TELA <= "000"; else TELA <= TELA + "001"; end if; end if; end if; end process ANIMACAO; |

Padrões

Um mutiplexador seleciona o tipo de padrão a ser mostrado no monitor a partir do valor (Tela) apresentado pelo contador.

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 144 145 146 147 148 149 150 151 152 153 154 155 156 157 158 159 160 161 162 163 164 165 166 167 168 169 170 171 172 173 174 175 176 177 178 179 180 181 182 183 184 185 186 187 188 189 190 191 192 193 194 195 196 197 198 199 200 201 202 203 204 205 206 207 208 209 210 211 212 213 214 215 216 217 218 219 220 221 222 223 224 225 226 227 228 229 230 231 232 233 234 235 236 237 238 239 |

PADROES: process(CLOCK2,CONT_X) begin case TELA is when "000" => if CONT_X <100 then RGB <= "001"; end if; if (CONT_X>=100 and CONT_X<200) then RGB <= "010"; end if; if (CONT_X>=200 and CONT_X<300) then RGB <= "011"; end if; if (CONT_X>=300 and CONT_X<400) then RGB <= "100"; end if; if (CONT_X>=400 and CONT_X<500) then RGB <= "101"; end if; if (CONT_X>=500) then RGB <= "110"; end if; when "001" => if CONT_X <100 then RGB <= "010"; end if; if (CONT_X>=100 and CONT_X<200) then RGB <= "011"; end if; if (CONT_X>=200 and CONT_X<300) then RGB <= "100"; end if; if (CONT_X>=300 and CONT_X<400) then RGB <= "101"; end if; if (CONT_X>=400 and CONT_X<500) then RGB <= "110"; end if; if (CONT_X>=500) then RGB <= "001"; end if; when "010" => if CONT_X <100 then RGB <= "011"; end if; if (CONT_X>=100 and CONT_X<200) then RGB <= "100"; end if; if (CONT_X>=200 and CONT_X<300) then RGB <= "101"; end if; if (CONT_X>=300 and CONT_X<400) then RGB <= "110"; end if; if (CONT_X>=400 and CONT_X<500) then RGB <= "001"; end if; if (CONT_X>=500) then RGB <= "010"; end if; when "011" => if CONT_X <100 then RGB <= "100"; end if; if (CONT_X>=100 and CONT_X<200) then RGB <= "101"; end if; if (CONT_X>=200 and CONT_X<300) then RGB <= "110"; end if; if (CONT_X>=300 and CONT_X<400) then RGB <= "001"; end if; if (CONT_X>=400 and CONT_X<500) then RGB <= "010"; end if; if (CONT_X>=500) then RGB <= "011"; end if; when "100" => if CONT_X <100 then RGB <= "101"; end if; if (CONT_X>=100 and CONT_X<200) then RGB <= "110"; end if; if (CONT_X>=200 and CONT_X<300) then RGB <= "001"; end if; if (CONT_X>=300 and CONT_X<400) then RGB <= "010"; end if; if (CONT_X>=400 and CONT_X<500) then RGB <= "011"; end if; if (CONT_X>=500) then RGB <= "100"; end if; when others => if CONT_X <100 then RGB <= "110"; end if; if (CONT_X>=100 and CONT_X<200) then RGB <= "001"; end if; if (CONT_X>=200 and CONT_X<300) then RGB <= "010"; end if; if (CONT_X>=300 and CONT_X<400) then RGB <= "011"; end if; if (CONT_X>=400 and CONT_X<500) then RGB <= "100"; end if; if (CONT_X>=500) then RGB <= "101"; end if; end case; end process PADROES; |

Outros blocos

Outros blocos, simulação e montagem do projeto são iguais ao projeto Padrão VGA.

Arquivos de Projeto

Para o download do projeto completo, clique aqui.

O arquivo está no formato “zip”, e inclui, entre outros:

– O arquivo de projeto do Quartus , no formato “.qpf”

– A descrição no formato VHDL , no formato”.vhd”

– O arquivo para gravação do CPLD, no formato “.pof”.

– O test bench utilizado na simulação , no formato “.vhd”