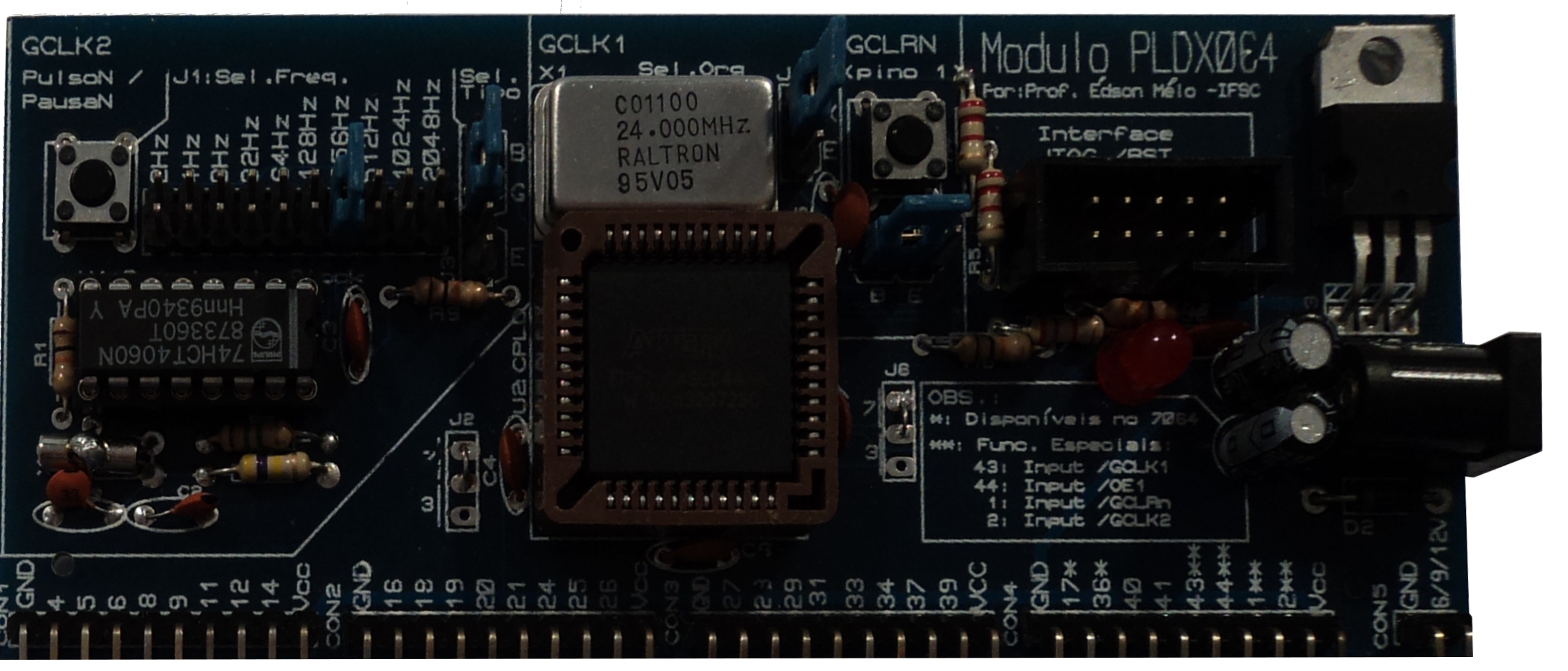

Módulo CPLD 7064

Introdução

Pensando em atender os requisitos de baixo custo, e simplicidade no desenvolvimento de aplicações desde as mais simples até as mais complexas, desenvolveu-se um módulo didático de CPLD baseado no componente EPM7064 pertencente a família de PLDs MAX 7000 da ALTERA.

A família de PLDs de alta densidade e alta performance MAX 7000, é baseada na segunda geração da arquitetura MAX da Altera Fabricados com uma avançada tecnologia CMOS, a família MAX 7000 é baseada em EEPROM e oferece de 600 a 5000 portas utilizável, ISP, e velocidade de até 175,4 MHz.

Características

- O CPLD utilizado é o EPM7064SLC44-10 alimentado em 5V, para sinais de Entrada e Saída com Lógica de 5V.

- Entrada de Alimentação externa de até 15V, regulador de tensão interno para 5V.

- Gravação via Interface JTAG, podendo-se utilizando as interfaces de gravação da ALTERA a Byteblaster ou USBblaster.

- Dois circuitos osciladores Independentes compostos de um oscilador de 24MHz e um oscilador de baixa frequência, que fornece multiplas frequências e é baseado no componente 74HCT4060

- Botão de Reset

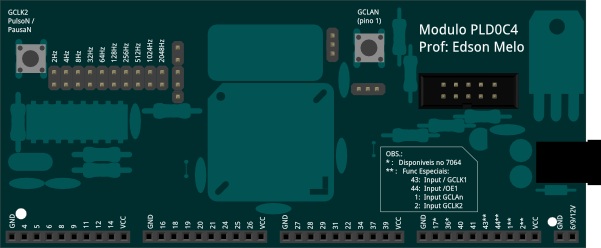

- Sinais de Entrada e Saída do PLD disponíveis em quatro conectores de 10 pinos, obedecendo a configuração: VCC + 8 pinos E/S + GND

Como pode ser observado na figura acima todos os pinos do CPLD, excluindo-se os pinos de VCC e GND, estão disponíveis em 4 conectores de 10 pinos, esta configuração foi utilizada de modo a facilitar a integração do Módulo de CPLD com os Módulos Periféricos do FPGA Para Todos.

Destes 40 pinos, 26 são pinos de uso geral, 8 pinos fornecem alimentação aos circuitos conectados ao módulo de CPLD e 4 pinos são reservados para funções especiais.

As funções especiais atribuídas a estes pinos são:

Pino 1: GCLRn Clear Global – Utilizado para reset geral do dispositivo.

Pino 2: GCLK2 – Clock Global 2 – pino utilizado para inserir sinal de clock no projeto.

Pino 43: /GCLK1 – Clock Global 1 – pino utilizado para inserir sinal de clock no projeto.

Pino 44: /OE1 – Pino de habilitação para saídas lógicas “tri-state”.

Uma pergunta que poderia ser feita neste momento:

– Mas para que dois pinos específicos para Clock? Eu não poderia utilizar qualquer pino para injetar o sinal de Clock?

A resposta é a seguinte;

– Você pode sim mapear outro pino para inserir o sinal de Clock. Existe a preferência por utilizar estes pinos pois os mesmos ja estão conectados a todas as macrocélulas do CPLD o que melhora o aproveitamento do projeto.

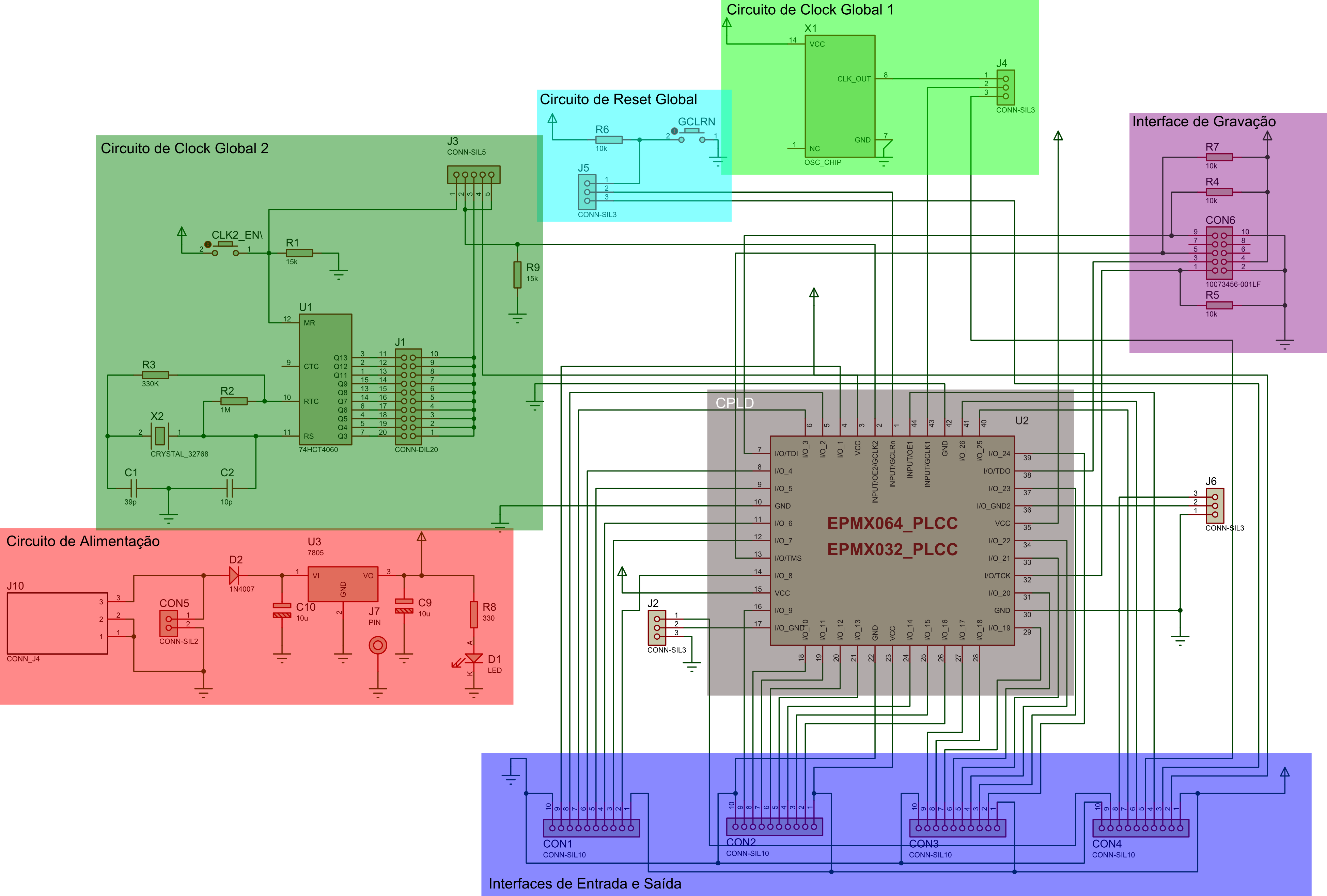

Diagrama Esquemático

O diagrama esquemático do Módulo de CPLD está dividido em 6 blocos, que serão apresentados abaixo.

Circuito de Alimentação

Como já foi mencionado anteriormente o módulo de CPLD pode ser alimentado com tensões entre 7,5 e 15 volts, estas limitações são devidas ao fato de o Módulo utilizar um regulador de tensão LM7805, que precisa de uma tensão diferencial de 2 volts entre a entrada e a saída (5V), e apesar de o 7805 suportar tensões de até 30 volts, recomenda-se não exceder 15 volts pois o regulador montado na placa não possui discipador e uma tensão superior pode provador um superaquecimento e uma possivel queima do componente.

Circuito de Reset

O circuito de reset é bem simples e é formado por um resistor de pull-up, para garantir que a entrada fique em nível alto, e um push-botton para GND, de modo a que a entrada vai a “ZERO” quando o botão é pressionado. O circuito tembém possui um jumper (J5) que permite selecionar se o reset será provocado pelo botão (J5 posição B) ou através do pino 1(GCLRn) (J5 posição E) como mencionado na descrição da placa principal.

|

|

| Jumper J5 na posição B, o Push-Botton GCLRN provoca o reset global do CPLD | Jumper J5 na posição E, o pino 1 presente no CON4 provoca o reset global do CPLD |

Circuitos de Clock

O Módulo de CPLD possui dois circuitos de Clock, um que fornece 24MHz e outro que o usuário pode selecionar uma entre 10 frequencias pre configuradas.

Clock Global 1 (GCLK1)

O circuito de Clock Global 1 é o resposável por fornecer o clock para o pino 43 do CPLD, através do Jumper J4 pode-se escolher entre utilizar o circuito fornecido com o módulo ou utilizar o pino 43 presente no CON4 da interface de entrada e saída do módulo.

Clock Global 2 (GCLK2)

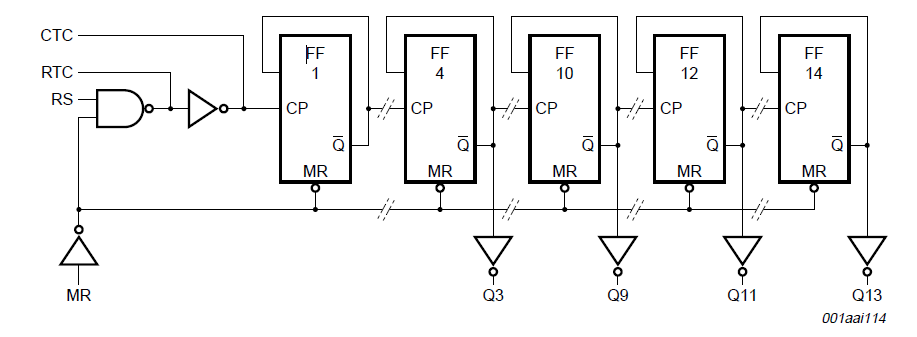

O cicuito de Clock Global 2 é baseado em um CI divisor de frequencias o 74HCT4060N que possui a seguinte configuração interna:

Utiliza-se um circuito oscilador de 32kHz como frequência base e o usuário pode escolher entre uma das 10 frequências de oscilação atravez do conector J1, é importante resaltar que o usuário não deve selecionar mais do que uma frequência simultaneamente, pois isto coloca as saídas do divisor de frequência em curto podendo provocar a queima do componente. As frequências selecionáveis são:

- 2Hz

- 4Hz

- 8Hz

- 32Hz

- 64Hz

- 128Hz

- 256Hz

- 512Hz

- 1024Hz

- 2048Hz

Optou-se por inserir este componente ao módulo de CPLD para que o usuário não precise utilizar macrocélulas do CPLD para realizar a divisão de frequência deixando mas espaço para as aplicações do usuário.

Além do conector J1, que permite selecionar a frequência desejada, o circuito de Clock Global 2 está equipado com um conector J3 que permite selecionar como o clock Global 2 ira interagir com o CPLD.

Na posição B o sinal do botão presente no circuito de clock é enviado ao CPLD funcionando como pulso de clock.

Na posição G o sinal do gerador de clock é enviado ao CPLD, nesta posição o clock enviado ao CPLD é o selecionado através do J1, e o botão funciona como uma pausa no clock.

Na posição E o sinal de clock pode ser enviado ao CPLD através do pino 2 do CON4, nesta opção o circuito de Clock Global 2 não tem efeito para o CPLD.

Cabo de Programação

O cabo “BaitaBlaster” que realiza a gravação via porta paralela apresentado abaixo

Fonte de Alimentação

A fonte de Alimentação ideal para ser utilizada com o módulo é de 7,5V 1,5A.

Exemplos de Aplicação

No portal tem disponíveis diversos exemplos de aplicações com essa placa de CPLD.