Decodificador Duplo para Display de Sete Segmentos

Neste projeto, expandimos o circuito do decodificador de binário para 7 segmentos estudado no artigo “Decodificador para Display de Sete Segmentos” para a exibição de dois algarismos. Para diversos algarismos, pode ser interessante um processo de multiplexação, como mostrado no artigo “Multiplexação Display de 6 Algarismos”.

A implementação do duplo decodificador, realizada aqui no modo esquemático do Quartus II, exemplifica um projeto hierárquico, que é construído a partir de blocos mais simples. A simulação deste projeto não será feita, pois ele é uma expansão de outro já simulado. No final deste exemplo há um tutorial sobre a implementação do modo hierárquico no Quartus® II, além de dicas sobre “Análise e Síntese”.

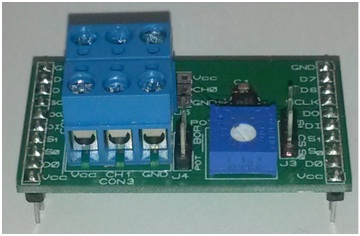

Neste projeto será utilizado:

- 1x Módulo CPLD_7064;

- 1x Placa de Chaves;

- 2x Placa de Display de Sete Segmentos de anodo comum.

Detalhamento da Estrutura

O circuito de um decodificador de binário para 7 segmentos é discutido e implementado em outro artigo do portal. Aqui, simplesmente agruparemos dois decodificadores para a exibição de um valor de oito bits, na forma de dois algarismos hexadecimais para exibição em displays.

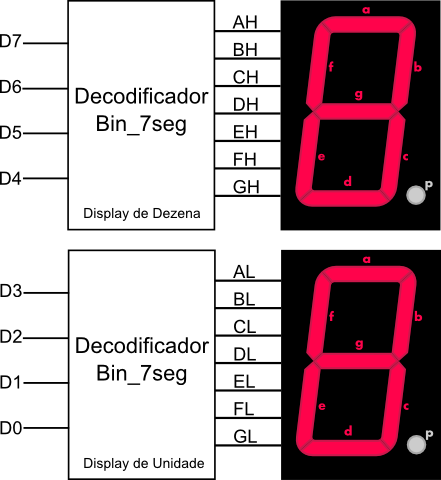

Figura 1 – Diagrama de Blocos

No Quartus II, o circuito implementado em modo esquemático pode ficar na forma mostrada na figura abaixo.

Figura 2 – Diagrama Esquemático no Quartus II

No diagrama esquemático, as oito entradas para o dado de oito bits (D7, D6,…,D0) são agrupadas em um símbolo único de pino. Se diz que os sinais de entrada formam o grupo (ou barramento) representado por D[7..0]. Os sinais do grupo podem ser utilizados individualmente no esquemático, e neste projeto são conectados às entradas dos blocos “bin_7seg“. D7 a D4 compõem a parte mais significativa do valor de oito bits, e são aplicadas a um dos decodificadores. O outro decodificador recebe a parte menos significativa, nos sinais D3 a D0.

Cada decodificador possui sete saídas, uma para cada segmento, e são nomeadas de AH à GH (para o display mais significativo) e de AL à GL (para o menos significativo), como mostra a Figura 2. Aqui, vamos adotar uma abordagem hierárquica de projeto: O bloco “bin_7seg“, desenvolvido anteriormente, será utilizado como um bloco básico do nosso novo circuito.

Implementação do Projeto

Inicialmente, crie uma nova pasta, de nome “duplo_dec” para o projeto, e copie para dentro dela os arquivos de diagrama esquemático e símbolo do bloco bin_7seg (arquivos bin_7seg.bdf e bin_7seg.bsf ilustrados na Figura 3).

Figura 3: Arquivos “.bdf” e “.bsf“

Execute o assistente para um novo projeto do Quartus. No segundo passo do assistente, Figura 4, adicione o arquivo do diagrama esquemático (“.bdf“) ao projeto.

Figura 4: Segundo Passo do Assistente do Quartus II

Após a conclusão do assistente, crie um novo diagrama esquemático para construir o mesmo. Na janela de seleção de componentes, Figura 5, observe que existe agora uma biblioteca “Projeto”, onde se encontra o bloco bin_7seg. Duas instâncias deste bloco serão utilizadas em nosso diagrama esquemático, como apresentado na Figura 2.

Figura 5: Bloco do Modo Hierárquico

Figura 5: Bloco do Modo Hierárquico

Após a conclusão da entrada do esquema, salve-o. Observe a característica de modo hierárquico: nosso circuito, na forma do duplo_dec.bdf, é o arquivo de topo de hierarquia do projeto. Esta hierarquia pode ser vista na janela do utilitário “Project Navigator” do Quartus II (Figura 6).

Figura 6: Hierarquia do Projeto

Depois de estruturar todo projeto, faça uma Análise e Síntese do mesmo para o programa procurar algum erro ou aviso no esquemático. Se não ocorreu nenhum equívoco na implementação do projeto, os mesmos dois avisos encontrados no “Decodificador para Display de Sete Segmentos” aparecerão: compilação paralela e da porta lógica “E” respectiva à combinação “oito” não usada. Para mais informações sobre esses avisos consulte o artigo sobre o “bin_7seg” (link aqui) e também o tutorial no final deste artigo.

Um resumo da Análise e Síntese está logo abaixo.

Figura 7: Resumo da Análise e Síntese

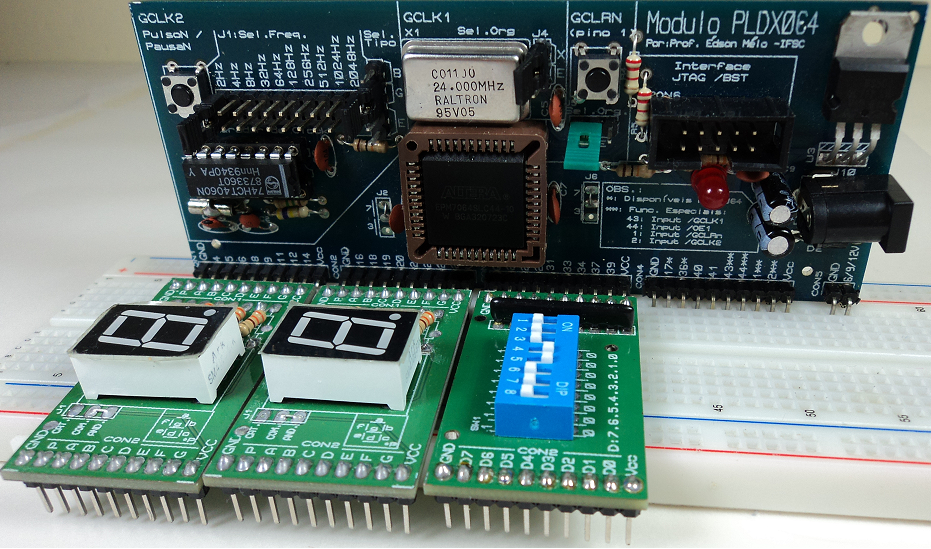

Estrutura Física

O projeto é composto pelo módulo de CPLD, duas placa de display de sete segmentos de anodo comum e outra de chaves, conectados respectivamente no CON1, CON2 e CON3 do CPLD, como mostra a Figura 8. A estrutura física foi selecionada de forma ergonômica: o display mais significativo fica acima do outro, e a chaves ficam abaixo dos displays. Lembre-se de que o CPLD usado é o EPM7064, da família MAX7000S.

No projeto, as entradas são implementadas pela placa de chaves, as saídas pelas placas de display e as funções lógicas pelo kit de CPLD.

Figura 8: Estrutura Física do Projeto

Montagem e Roteamento

Fique atento para que o Vcc e o GND dos periféricos fiquem alinhados com o do CPLD. Veja em detalhe a ilustração da montagem do projeto, feita no Fritzing, na Figura 9.

Figura 9: Ligação na Matriz de Contatos

A Figura 10 mostra a pinagem atribuida no Pin Planner, no Quartus II, de acordo com a ligação na matriz de contatos.

Figura 10: Atribuição dos Pinos no Pin Planner

Gravação e Teste

Depois de implementar e atribuir os pinos do projeto, faça uma “Compilação Completa” para gerar o arquivo de gravação do projeto, além do programa procurar algum erro ou aviso no mesmo.

Para gravar o projeto siga o Tutorial de Criação de Projeto em Modo Esquemático na etapa de “Gravação do CPLD” clicando aqui. Lembre-se sempre de gravar o módulo de CPLD sem os periféricos, evitando problemas na pinagem atribuída em projetos anteriores. Também não esqueça de configurar as saídas não utilizadas como entradas tri-state.

Para testar o funcionamento desse projeto, monta-se a periferia como relatada na “Estrutura Física” e atribuem-se níveis lógicos na placa de chaves, analisando a combinação posta com a decodificação em cada display de sete segmentos. O vídeo na introdução desse exemplo apresenta o teste realizado.

Tutorial – Implementação do Modo Hierárquico

Segue abaixo o tutorial sobre a implementação do projeto:

Arquivos do projeto

Para o download do projeto completo, clique aqui.

O arquivo está no formato “.zip”, e inclui os arquivos de projeto do Quartus (“.qpf”), de modo esquemático (“.bdf”), de gravação do CPLD (“.pof”), de símbolo para usar em projetos mais avançados (“.bsf”), entre outros.

Referências