Padrão de Cores VGA

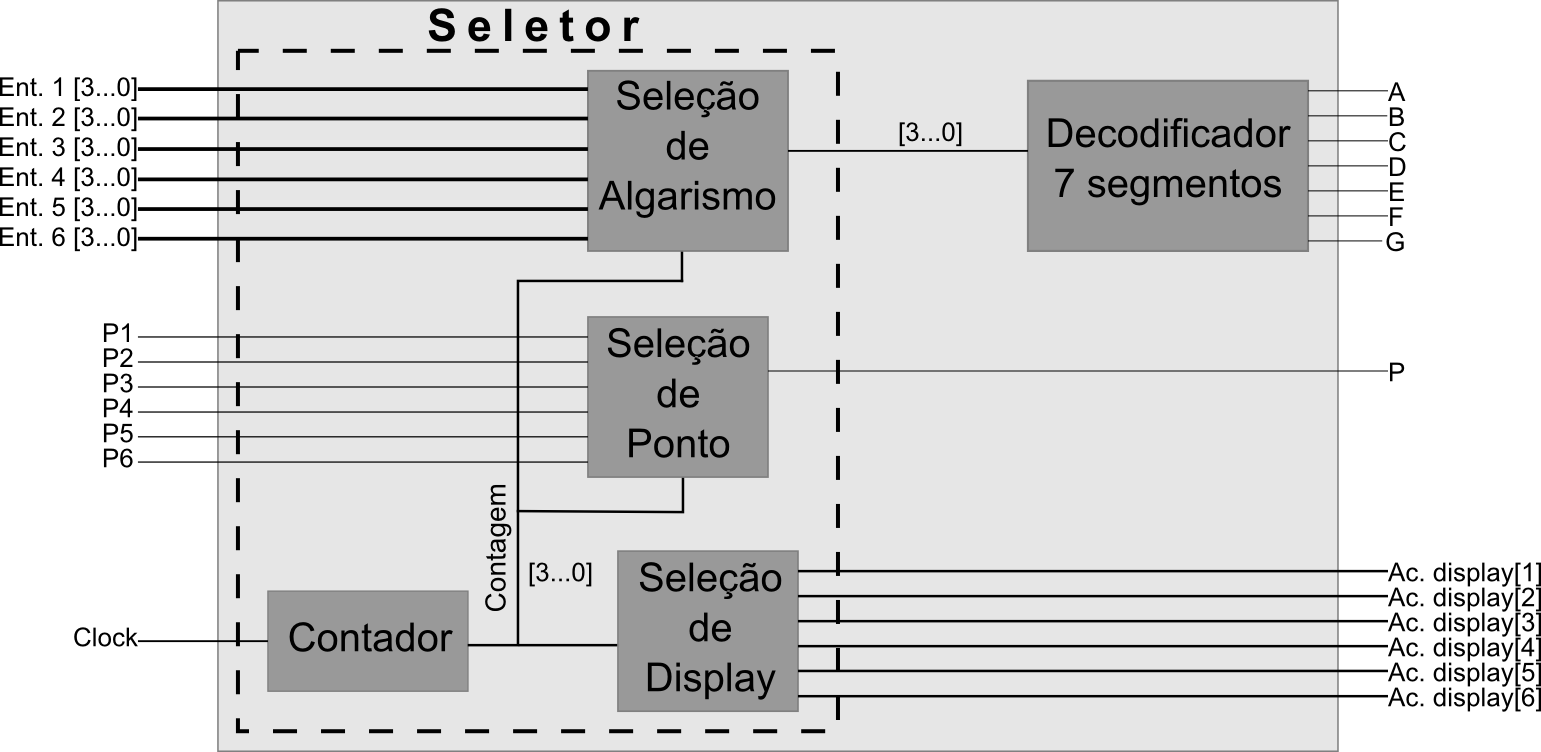

No modo VGA a tela é dividida em pontos (pixels) que são separados por linhas e colunas. Geralmente a imagem possui 480 linhas e 600 colunas e somente um pixel é aceso de cada vez. Para formarmos uma tela, utilizamos o efeito da persistência da visão, utilizado também no projeto Multiplexação de display de 6 algarismos.

O projeto descrito a seguir é um exemplo de circuito lógico sequencial, descrito em VHDL e simulado software ModelSim®-Altera, utilizando um testbench.

Os equipamentos necessários para a implementação do projeto são:

- 1x Kit CPLD 7064;

- 1x Monitor com porta VGA;

- 1x Placa de interface VGA;

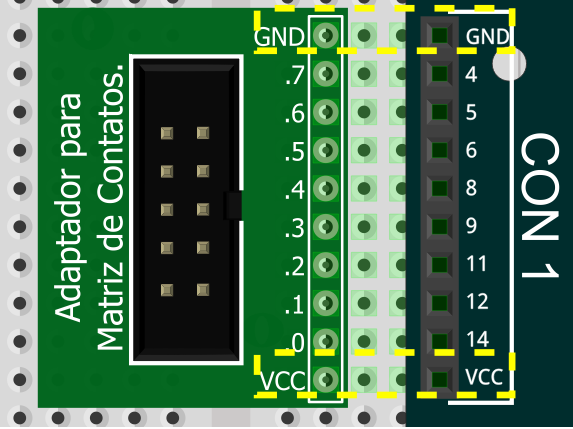

- 1x Adaptador para matriz de contatos

Lógica de Funcionamento

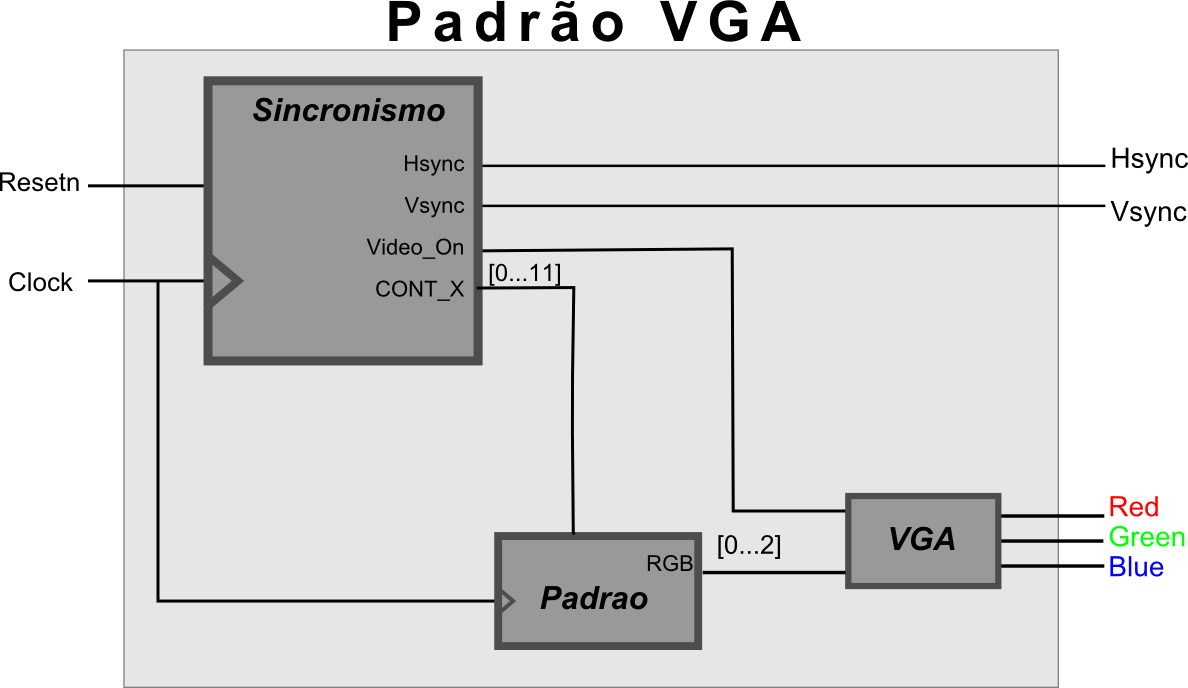

Este projeto é descrito da seguinte forma:

A fim de melhorar a explicação do projeto, o mesmo foi divididos em blocos. Cada bloco funciona da seguinte maneira:

Sincronismo

O bloco possui um contador que marca os pulsos de clock para enviar os pulsos de sincronismo no tempo certo. O kit de CPLD possui um clock de 24MHz.

Para a contagem de pixels temos:

| Tempo (us) | Pulsos de Clock |

| 25,17 | 604 |

| 26,11 | 627 |

| 29,88 | 717 |

| 31,77 | 762 |

Em VHDL fica:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 |

If (CONT_X >= H_max) then -- H_max = 762 CONT_X <= (others=>'0'); else CONT_X <= CONT_X + "000000000001"; end if; If (CONT_X <= 717) and (CONT_X >= 627) then -- Ajusta o tempo de Horiz_Sync Horiz_Sync <= '0'; else Horiz_Sync <= '1'; end if; if (CONT_X <= 604) then -- Ajusta o tempo de VIDEO_ON_H VIDEO_ON_H <= '1'; else VIDEO_ON_H <= '0'; end if; |

Para contagem de Linhas temos:

| Tempo(ms) | Contagem de Linhas |

| 15,250 | 480 |

| 15,700 | 494 |

| 15,764 | 496 |

| 16,764 | 528 |

Em VHDL temos:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 |

If (CONT_Y >= V_max) and (CONT_X = 299) then CONT_Y <= "000000000000"; else If (CONT_X = H_MAX) then CONT_Y <= CONT_Y + "000000000001"; end if; end if; If (CONT_Y <= 495) and (CONT_Y >= 493) then Vert_Sync <= '0'; else Vert_Sync <= '1'; end if; If (CONT_Y <= 480) then VIDEO_ON_V <= '1'; else VIDEO_ON_V <= '0'; end if; |

Estes tempos foram retirados de análises anteriores. Mais informações sobre a temporização e pulsos de sincronismo, veja o projeto VGA para FPGA.

Padrão

O bloco possui um decodificador que faz o padrão de cores na tela. Através da contagem de pixels, ele reconhece em que faixa do monitor está sendo escrita.

em VHDL temos:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 |

PADRAO: process(CLOCK) begin if CONT_X <100 then RGB <= "001"; end if; if (CONT_X>=100 and CONT_X<200) then RGB <= "010"; end if; if (CONT_X>=200 and CONT_X<300) then RGB <= "011"; end if; if (CONT_X>=300 and CONT_X<400) then RGB <= "100"; end if; if (CONT_X>=400 and CONT_X<500) then RGB <= "101"; end if; if (CONT_X>=500) then RGB <= "110"; end if; end process PADRAO; |

VGA

Este bloco serve simplesmente para saber se o padrão será enviado ou está dentro do periodo de branqueamento.

Em VHDL:

|

1 2 3 4 5 6 7 8 9 10 11 12 |

VGA: process(CLOCK) begin if VIDEO_ON = '1' then RED <= RGB(0); GREEN <= RGB(1); BLUE <= RGB(2); else RED <= '0'; GREEN <= '0'; BLUE <= '0'; end if; end process VGA; |

Simulação

A simulação utiliza um Testbench de forma bem simples. Simula apenas o clock e observa os sinais que são enviados ao monitor

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 |

geraclock: process begin clock <= '0'; -- Na partida, zera sinal de clock... wait for 20.83ns; -- Agora, comeca a oscilar: for cont in 0 to 2500000 loop clock <= not clock; wait for 20.83ns; end loop; wait; -- Parando este processo... end process; comportamento: process begin RESETn <= '0'; wait for 50 ns; RESETn <= '1'; wait for 300 us; wait; end process; |

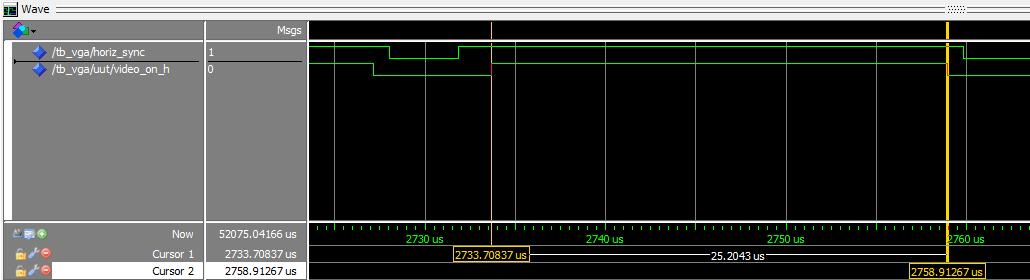

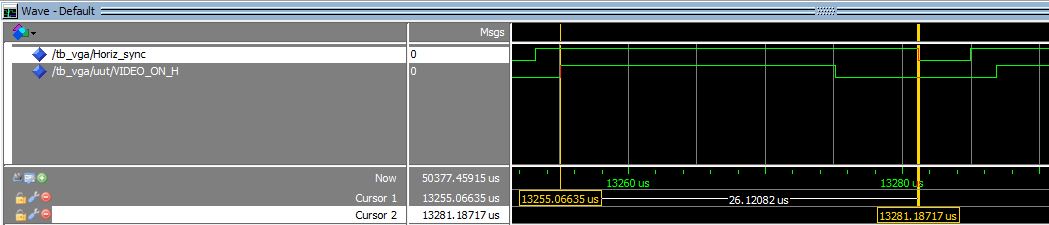

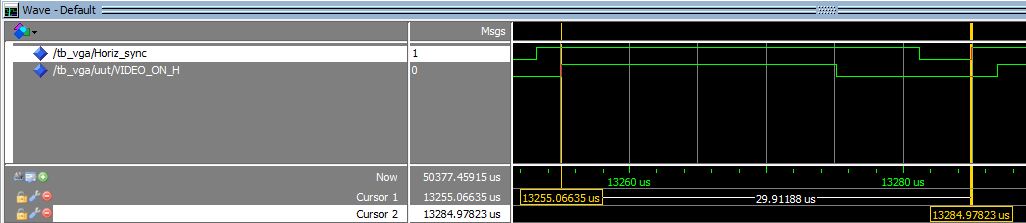

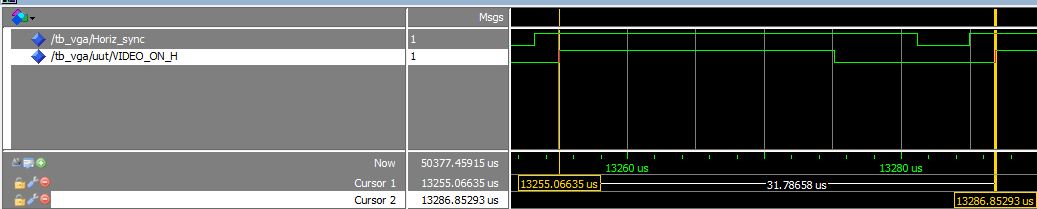

Estas imagens apresentam os resultados da simulação, clique nelas para ampliá-las :

Sincronismo Horizontal

Tempo de descida VIDEO_ON_H.

Tempo de descida VIDEO_ON_H.

Tempo de descida HSYNC

Tempo de descida HSYNC

Tempo de subida HSYNC

Tempo de subida HSYNC

Tempo de subida VIDEO_ON_H

Tempo de subida VIDEO_ON_H

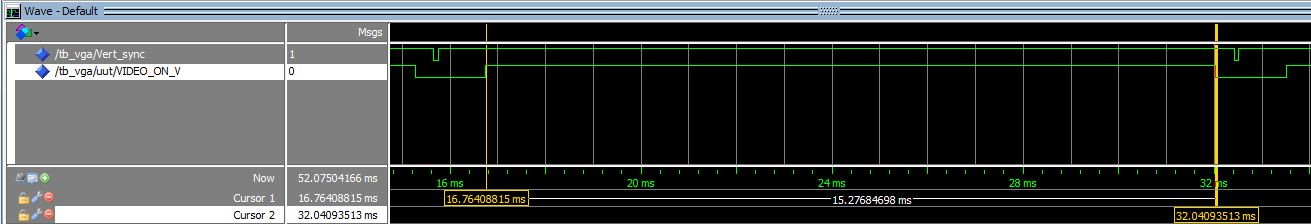

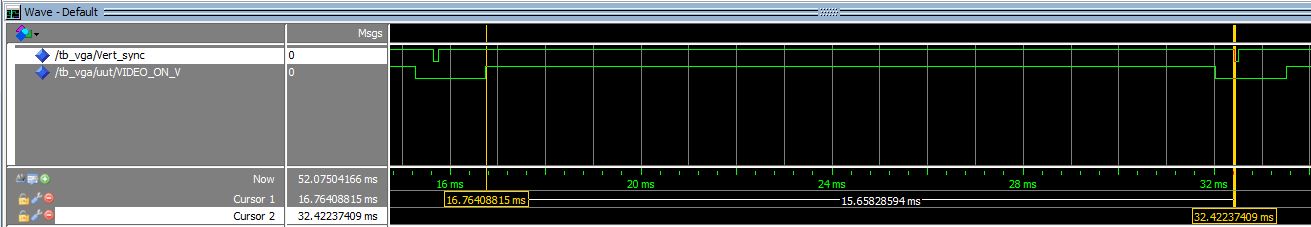

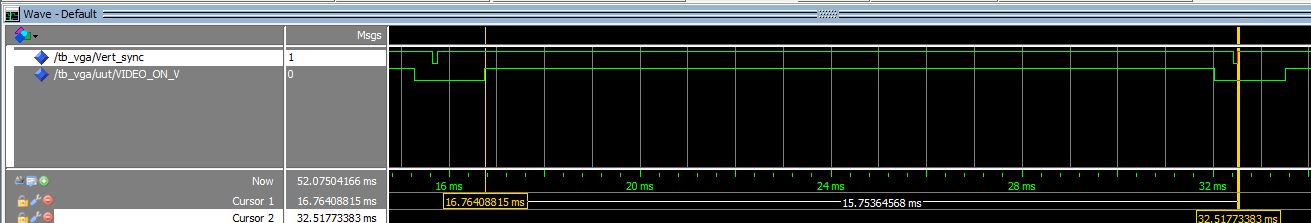

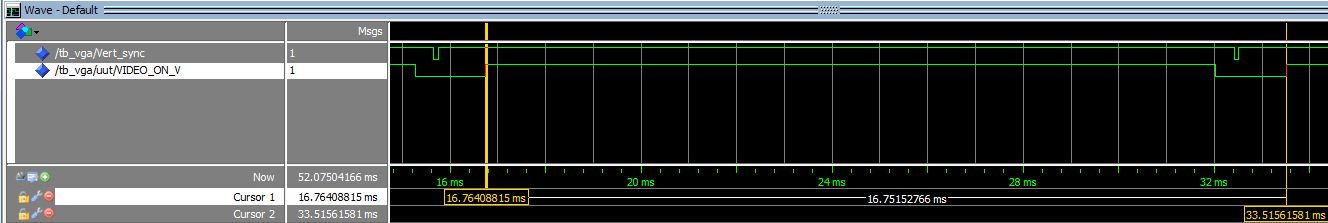

Sincronismo Vertical

Tempo de descida VIDEO_ON_V

Tempo de descida VIDEO_ON_V

Tempo de descida VSYNC

Tempo de descida VSYNC

Tempo de subida VSYNC

Tempo de subida VSYNC

Tempo de subida VIDEO_ON_V

Tempo de subida VIDEO_ON_V

Montagem e Roteamento

A imagem abaixo apresenta como deve ser montado o adaptador.

Arquivos do Projeto

Para o download do projeto completo, clique aqui.

O arquivo está no formato “zip”, e inclui, entre outros:

– O arquivo de projeto do Quartus , no formato “.qpf”

– A descrição no formato VHDL , no formato”.vhd”