Introdução

Os LEDs RGB são bem conhecidos e possuem diversas aplicações em sistemas eletrônicos. É possível encontrar muitas páginas da internet e artigos que descrevem exaustivamente as mais variadas aplicações e utilidades dos LEDs para a geração de efeitos luminosos, programados em populares plataformas de programação para computação (como Arduínos e Raspberry Pis), o controle da luminosidade de um LED pode ser feito com o uso de uma Modulação de Largura de Pulso (PWM), como descrito neste outro artigo. No artigo referenciado, descreve-se um projeto que permite aumentar ou diminuir a luminosidade de um LED a partir do comando de dois botões.

Neste projeto, um bloco de código VHDL é utilizado para controle via PWM, dos três componentes de cor de um LED RGB, podendo-se compor da forma desejada, uma cor qualquer dentro do espectro de cores atingido pelo LED. O software Quartus II Web Edition foi utilizado para geração dos blocos do projeto e do código VHDL e o kit de CPLD baseado no componente MAXV para testar a aplicação em hardware. O funcionamento do sistema é mostrado no clipe de vídeo disponível acima.

Hierarquia e Lógica de Funcionamento do Sistema

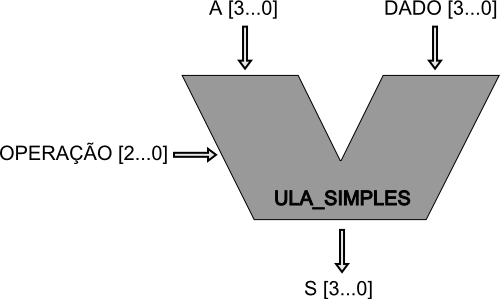

Deseja-se fazer o controle individual, da intensidade dos componentes de cor do LED RGB, que são na verdade três LEDs de cores vermelho, verde e azul, de modo a poder gerar qualquer cor. Os três blocos de PWM, permitem controlar a intensidade de cada cor e podem ser controlados pelo bloco CONTROLE_CORES, onde um conjunto de botões é continuamente verificado (servindo com IHM). O desenvolvimento deste projeto se caracterizou por uma abordagem hierárquica, em que blocos desenvolvidos e testados separadamente são agrupados para a composição de um sistema completo. Os seguintes componentes fazem parte da estrutura do projeto:

- GERA_CLOCKS, controla a geração dos sinais de clock CLK_IHM e CLK_PWM;

- CONTROLE_CORES, gerencia a seleção da cor e a razão cíclica dos LEDs;

- MODULO_PWM, define a intensidade luminosa para um LED.

A figura abaixo mostra o diagrama de blocos do projeto:

Figura 1 – Diagrama de Blocos

É possível observar na figura 1, a presença de três instâncias controladas por módulo PWM (uma para cada LED). E a animação a seguir representa um pequeno teste do projeto, onde os botões são pressionados (à esquerda), a bola verde informa qual LED esta selecionado e o resultado é exibido pelas formas de onda (à direita) que representam a razão cíclica da luz dos LEDs RGB:

Figura 2 – Animação

Descrição dos Blocos do Projeto

A seguir apresentamos uma introdução básica do sistema destacando alguns trechos de código.

GERA_CLOCKS:

O clock do kit de CPLD possui uma frequência de 24MHz, valor demasiadamente alto para o projeto. Sendo assim, utilizaremos um bloco de prescaler, um divisor de frequência que a partir da entrada de clock do sistema gera os sinais CLK_IHM e CLK_PWM, de menor frequência, que irão sincronizar a monitoração do estado dos botões e o efeito do PWM sobre os sinais de cor do LED. A arquitetura, em VHDL, para o GERA_CLOCKS é mostrado abaixo.

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 |

---------------- Arquitetura ---------------- architecture COMPORTAMENTO of GERA_CLOCKS is begin GERADOR_CLOCKS: process(CLK, RSTn, CLK_ENABLE) variable cnt1: integer range 0 to FATOR_PRESCALER +2; variable cnt2: integer range 0 to FATOR_IHM +2; begin if RSTn = '0' then cnt1 :=0; cnt2 :=0; CLK_IHM <= '0'; CLK_PWM <= '0'; elsif rising_edge(CLK) and CLK_ENABLE = '1' then cnt1 := cnt1 +1; if cnt1 = FATOR_PRESCALER then CLK_PWM <= not CLK_PWM; cnt1 :=0; cnt2 := cnt2 +1; if cnt2 = FATOR_IHM then CLK_IHM <=not CLK_IHM; cnt2 :=0; end if; end if; end if; end process GERADOR_CLOCKS; end architecture COMPORTAMENTO; |

Observe que o princípio de funcionamento é bastante simples, sendo descrito a seguir:

O sinal de entrada RSTn é um reset ativo em baixo, e deve ser momentaneamente baixo na partida do sistema, ou quando se deseja reiniciar o sistema.

O sinal CLK_ENABLE, quando em nível alto, habilita o divisor de frequência.

A divisão de frequência é realizada a partir de duas contagens, nas variáveis cnt1 e cnt2, respectivamente associadas aos sinais de saída CLK_PWM e CLK_IHM.

A contagem em cnt1 vai de 0 a 200.000, quando se inverte o estado na saída CLK_PWM. Em duas destas contagens, CLK_PWM completa um período. Sendo assim, sua saída deve ter um período de:

2 * 200.000 * (1/ 24 MHz) = ~16,67 ms, e uma frequência de 1/16.67 ms = 60 Hz.

A contagem em cnt2 é incrementada a cada transição de subida de CLK_PWM, até atingir 15, quando se inverte o estado de CLK_IHM. Assim, em dois ciclos de contagem de cnt2, ou seja, em 30 períodos de CLK_PWM obtem-se um período de CLK_IHM. A duração deste período é de:

2*15*200.000*(1/24 MHz) = 0,25 s, correspondente a uma frequência de 4Hz.

No bloco CONTROLE_CORES, este valor implica em que os botões do sistema serão verificados quatro vezes por segundo.

DECLARAÇÃO:

Entre o begin e a architecture do arquivo de topo do projeto (rgb_teste.vhd), é necessário inserir a declaração do componente. A seguir, a declaração do componente GERA_CLOCKS, em VHDL:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 |

-- Declaração do gerador de clocks: component GERA_CLOCKS generic ( FATOR_IHM : INTEGER := 200000; FATOR_PRESCALER : INTEGER := 15 ); port ( CLK : IN STD_LOGIC; CLK_ENABLE : IN STD_LOGIC; RSTn : IN STD_LOGIC; CLK_IHM : OUT STD_LOGIC; CLK_PWM : OUT STD_LOGIC ); end component; |

a, sans-serif;”>E a tabela abaixo classifica as portas especificando suas funções:

| Nome da Porta | Tipo | Definição |

| CLK | Entrada | Contém o valor do sinal de clock do kit. |

| CLK_ENABLE | Entrada | Ativa ou desativa o componente. |

| RSTn | Entrada | Botão de reset negado. |

| CLK_IHM | Saída | Sinal de clock gerado. |

| CLK_PWM | Saída | Sinal de clock gerado. |

INSTANCIAÇÃO:

Entre o begin e o fim da architecture do arquivo de topo do projeto (rgb_teste.vhd), é preciso inserir a instanciação do componente. A seguir, a instanciação do componente GERA_CLOCKS, em VHDL:

|

1 2 3 4 5 6 7 8 9 10 11 |

-- Instanciação do gerador de clocks: GERA_CLOCKS_Inst: GERA_CLOCKS port map ( CLK => CLK, CLK_ENABLE => '1', RSTn => RSTn, CLK_IHM => CLK_IHM, CLK_PWM => CLK_PWM ); |

A seguinte tabela classifica as portas, especificando a que sinal cada uma delas é atribuída:

| Nome da Porta | Atribuíção | Justificação |

| CLK | CLK | O sinal de clock do componente possui o mesmo valor de CLK (sinal de clock do kit). |

| CLK_ENABLE | ‘1’ | A função desta porta é ativar ou desativar o prescaler, neste projeto, seu valor será sempre ‘1’ (habilitada). |

| RSTn | RSTn | O valor deste sinal é o mesmo do botão reset negado. |

| CLK_IHM | CLK_IHM | Sinal de saída. |

| CLK_PWM | CLK_PWM | Sinal de saída. |

CONTROLE_CORES:

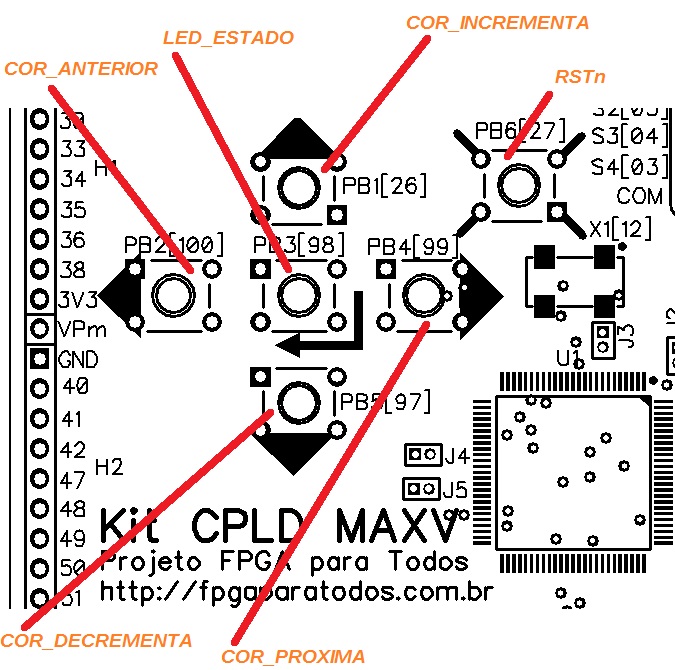

Este bloco representa a IHM do projeto, e é responsável por verificar o estado dos botões e gerar os sinais de comando que são interpretados pelos módulos PWM para efetuar o controle das cores. A Figura 3 representa os botões da placa que serão utilizados:

Figura 3 – Botões no Kit

Diferentemente do componente anterior, este bloco não utiliza o sinal de clock do kit para executar sua função, mas utiliza o sinal de clock CLK_IHM que possui uma frequência de 60Hz, gerada no processo GERADOR_CLOCKS do componente GERA_CLOCKS. Este valor de frequência foi escolhido porque é adequado para que o usuário não perceba o “pisca-pisca” dos LEDs. Neste componente há apenas um processo, denominado testa_botoes, onde são feitas as checagens dos botões do kit. A seguir uma lista das funções de cada botão:

- COR_ANTERIOR: Seleciona a cor anterior da lista.

- COR_PROXIMA: Seleciona a próxima cor da lista.

- COR_MAIS: Aumenta a razão cíclica.

- COR_MENOS: Diminui a razão cíclica.

- LED_ESTADO: Apaga os LEDs, entretanto, quando liberado, retorna todas as configurações anteriores.

- RSTn: Altera a cor selecionada para a inicial (azul), e a razão cíclica dos LEDs para 0%.

Observação: Os botões são verificados na borda de subida do clock CLK_IHM, exceto RSTn, pois não necessita de um sinal de clock.

Após as checagens dos botões, o processo testa_botoes gera três sinais, PWM_VERMELHO, PWM_VERDE e PWM_AZUL, valores de oito bits, cada um deles definindo a razão cíclica de seu respectivo LED. Abaixo, o código em VHDL, utilizado para gerar os três sinais:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 |

------------------ Arquitetura ------------------ architecture COMPORTAMENTO of CONTROLE_CORES is type ESPACO_RGB is array (2 downto 0) of std_logic_vector (7 downto 0); signal DT_COR : ESPACO_RGB; begin testa_botoes: process (CLK, HABILITA_CLK, RSTn) variable select_cor: integer range 0 to 5 := 0; variable var_cor : ESPACO_RGB; begin if ( RSTn = '0') then select_cor := 0; var_cor (2):= X"00"; var_cor (1):= X"00"; var_cor (0):= X"00"; elsif rising_edge (CLK) and HABILITA_CLK = '1' then if ( COR_ANTERIOR = '0') then if( select_cor = 0) then select_cor:= 2; else select_cor := select_cor - 1; end if; end if; if ( COR_PROXIMA = '0') then select_cor := select_cor + 1; if ( select_cor = 3 ) then select_cor := 0; end if; end if; if COR_MAIS = '0' then if var_cor (select_cor) < X"FF" then var_cor (select_cor) := var_cor (select_cor) + X"05"; end if; end if; if COR_MENOS = '0' then if var_cor (select_cor) > X"00" then var_cor (select_cor) := var_cor (select_cor) - X"05"; end if; end if; end if; case select_cor is -- Define que LED acender. when 0 => SEL_LEDS <= "001"; when 1 => SEL_LEDS <= "010"; when others => SEL_LEDS <= "100"; end case; DT_COR <= var_cor; end process testa_botoes; -- Passa a "quantidade de cor para os respectivos PWM's". PWM_VERMELHO <= DT_COR (2) when LED_ESTADO = '1' else X"00"; PWM_VERDE <= DT_COR (1) when LED_ESTADO = '1' else X"00"; PWM_AZUL <= DT_COR (0) when LED_ESTADO = '1' else X"00"; end architecture; |

Primeiramente a porta RSTn é verificada. Se RSTn estiver com o valor zero (ou seja, o botão esta sendo apertado), a variável select_cor é alterada para zero (então a cor selecionada passa a ser azul), e o vetor de três bits var_cor têm todos os seus valores alterados para zero, modificando a razão cíclica de todos os LEDs para 0%.Se RSTn for diferente de zero, então será checada a borda de subida de CLK_IHM e o valor do sinal HABILITA_CLK. Na subida de clock, se habilitado, as seguintes instruções poderão ser executadas:

- Se COR_ANTERIOR estiver pressionado, a variável select_cor será decrementada, selecionando uma nova cor.

- Se COR_PROXIMA estiver pressionado, a variável select_cor será incrementada, selecionado uma nova cor.

- Se COR_MAIS estiver pressionado, a variável var_cor correspondente à cor selecionada é aumentada em 5 unidades, até o máximo de 255. Desta forma, aumenta-se a intensidade luminosa de um dos componentes de cor do LED.

- Se COR_MENOS estiver pressionado a variável var_cor é subtraída em 5 unidades, até o mínimo de 0. Desta forma, aumenta-se a intensidade luminosa de um dos componentes de cor do LED.

Quando os botões COR_MAIS ou COR_MENOS são pressionados, a variável que representa a razão cíclica do respectivo LED é modificada em 05 na faixa entre 0 e 255. Como a frequência deste bloco é de 4Hz, cada segundo que um destes botões permanecer pressionado, resultará num aumento/subtração de 20 unidades.

DECLARAÇÃO:

Entre o begin e a architecture do arquivo de topo do projeto (rgb_teste.vhd), é necessário inserir-se a declaração do componente. A seguir, a declaração do componente CONTROLE_CORES, em VHDL:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 |

-- Declaração do controlador de cores: component CONTROLE_CORES port ( CLK : IN STD_LOGIC; HABILITA_CLK : IN STD_LOGIC; RSTn : IN STD_LOGIC; COR_MAIS : IN STD_LOGIC; COR_MENOS : IN STD_LOGIC; COR_PROXIMA : IN STD_LOGIC; COR_ANTERIOR: IN STD_LOGIC; LED_ESTADO : IN STD_LOGIC; PWM_VERMELHO : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); PWM_VERDE : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); PWM_AZUL : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); SEL_LEDS : OUT STD_LOGIC_VECTOR(2 DOWNTO 0) ); end component; |

A seguinte tabela classifica as portas especificando a que sinais cada uma é atribuída:

| Nome da Porta | Tipo | Definição |

| CLK | Entrada | Contém o valor do sinal de clock do componente. |

| HABILITA_CLK | Entrada | Ativa ou desativa o componente. |

| RSTn | Entrada | Botão de reset negado. |

| COR_MAIS | Entrada | Botão que incia as instruções de incremento da intensidade da luz dos LEDs. |

| COR_MENOS | Entrada | Botão que incia as instruções de decremento da intensidade da luz dos LEDs. |

| COR_MENOS | Entrada | Botão que inicia as instruções de seleção da próxima cor. |

| COR_ANTERIOR | Entrada | Botão que inicia as instruções de seleção da cor anterior. |

| LED_ESTADO | Entrada | Botão que desliga o LED, enquanto pressionado, e que, quando despressionado, não perde suas configurações anteriores. |

| PWM_VERMELHO | Saída | Contém o valor da razão cíclica do LED vermelho. |

| PWM_VERDE | Saída | Contém o valor da razão cíclica do LED verde. |

| PWM_AZUL | Saída | Contém o valor da razão cíclica do LED azul. |

| SEL_LEDS | Saída | Vetor de 3 bits que contém os LEDs RGB que serão acessos. |

INSTANCIAÇÃO:

Entre o begin e o fim da architecture do arquivo de topo do projeto (rgb_teste.vhd), é preciso inserir a instanciação do componente. A seguir, a instanciação do componente CONTROLE_CORES, em VHDL:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 |

-- Instanciação do controle de cores: CONTROLE_CORES_Inst: CONTROLE_CORES port map ( CLK => CLK_IHM, HABILITA_CLK => '1', RSTn => RSTn, COR_MAIS => COR_MAIS, COR_MENOS => COR_MENOS, COR_PROXIMA => COR_PROXIMA, COR_ANTERIOR => COR_ANTERIOR, LED_ESTADO => LED_ESTADO, PWM_VERMELHO => PWM_VERMELHO, PWM_VERDE => PWM_VERDE, PWM_AZUL => PWM_AZUL, SEL_LEDS => SEL_LEDS ); |

A seguinte tabela classifica as portas, especificando a que sinal cada uma delas é atribuída:

| Nome da Porta | Atribuição | Justificação |

| CLK | CLK_IHM |

O sinal de clock deste componente possui o valor do sinal de clock CLK_IHM. |

| HABILITA_CLK | ‘1′ | A função desta porta é ativar ou desativar o sinal de clock, neste projeto, seu valor será sempre ‘1’ (habilitada). |

| RSTn | RSTn |

O valor deste sinal é o mesmo do botão reset negado. |

| COR_MAIS | COR_MAIS |

Valor do botão (pressionado ou não). |

| COR_MENOS | COR_MENOS | Valor do botão (pressionado ou não). |

| COR_PROXIMA | COR_PROXIMA | Valor do botão (pressionado ou não). |

| COR_ANTERIOR | COR_ANTERIOR | Valor do botão (pressionado ou não). |

| LED_ESTADO | LED_ESTADO | Valor do botão (pressionado ou não). |

| PWM_VERMELHO | Saída | Valor de 8 bits que contêm a intensidade luminosa do LED vermelho. |

| PWM_VERDE | Saída | Valor de 8 bits que contêm a intensidade luminosa do LED verde. |

| PWM_AZUL | Saída | Valor de 8 bits que contêm a intensidade luminosa do LED azul. |

| SEL_LEDS | Saída | Define que LEDs acenderam. |

MODULO_PWM

Este é um bloco previamente desenvolvido, que gera um sinal PWM. Neste projeto, são utilizadas três instâncias deste componente, uma para cada cor básica (Vermelho, Verde e Azul).

O bloco MODULO_PWM tem três entradas: clock, TAXA e PRESCALER.

- A entrada TAXA, de oito bits configura a razão cíclica para o sinal de saída PWM, variando de 0% (quando TAXA for zero) a 100% (quando TAXA for “255”).

- A entrada PRESCALER configura um divisor de frequência para o clock de entrada. Nesta aplicação, com a entrada PRESCALER em zero, o prescaler é desabilitado, e o sinal de clock de entrada determina a frequência do sinal de saída.

- clock é o clock geral do sistema.

O PWM é gerado através de uma variável de contagem de oito bits, que varia de zero a “255”, sendo incrementada a cada borda de subida do clock de entrada, e zerada instantaneamente ao chegar a “255”. A saída de PWM transita para nível lógico alto quando a contagem é zerada, e para nível lógico baixo quando se iguala ao valor contido em TAXA, ou seja, a frequência do sinal de saída é “1/255” da frequência do clock de entrada, como mostrado na figura abaixo.

A saída do processo GERA_PWM do código é o sinal PRE_PWM, que é transferido à saída PWM do bloco se HABILITA for ‘1’ e INV_PWM zero. Neste projeto estes sinais são constantes, atendendo a ambas as condições, e o PWM é sempre habilitado.

A seguir o arquitetura de GERA_PWM:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 |

------------------ Arquitetura ------------------ architecture comportamento of modulo_pwm is signal PRESC_ENABLE : std_logic; signal PRE_PWM : std_logic; begin gera_prescaler: process (CLK, RSTn, PRESCALER, HABILITA) variable cont_prescaler : std_logic_vector (7 downto 0) := X"00"; variable hab_prescaler : std_logic := '0'; begin if ( HABILITA = '0' ) then hab_prescaler := '0'; else if (RSTn = '0') then cont_prescaler := X"00"; elsif rising_edge (CLK) and PRESCALER /= X"00" then cont_prescaler := cont_prescaler + 1; if ( cont_prescaler = PRESCALER) then cont_prescaler := X"00"; end if; end if; if (cont_prescaler = X"00") then hab_prescaler := '1'; else hab_prescaler := '0'; end if; end if; PRESC_ENABLE <= hab_prescaler; end process; gera_pwm: process (CLK, RSTn, PRESC_ENABLE) variable CONTAGEM : std_logic_vector ( 7 downto 0) := X"00"; variable SAIDA_PWM : std_logic := '0'; begin if ( RSTn = '0') then CONTAGEM := X"00"; SAIDA_PWM := '0'; elsif ( rising_edge (CLK) and PRESC_ENABLE = '1') then if ( '0' & taxa = CONTAGEM) then SAIDA_PWM := '0'; elsif ( CONTAGEM = X"00" ) then SAIDA_PWM := '1'; end if; CONTAGEM := CONTAGEM + 1; if CONTAGEM = X"FF" then CONTAGEM := X"00"; end if; end if; PRE_PWM <= SAIDA_PWM; end process; ajusta_saida: PWM <= PRE_PWM when INV_PWM = '0' and HAB_SAIDAn = '0' else not PRE_PWM when INV_PWM = '1' and HAB_SAIDAn = '0' else 'Z'; end architecture comportamento; |

DECLARAÇÃO:

Entre o begin e a architecture do arquivo de topo do projeto (rgb_teste.vhd) é necessário inserir a declaração do componente. A seguir, a declaração do componente MODULO_PWM, em VHDL:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 |

component MODULO_PWM port ( CLK : IN STD_LOGIC; RSTn : IN STD_LOGIC; HABILITA : IN STD_LOGIC; INV_PWM : IN STD_LOGIC; HAB_SAIDAn : IN STD_LOGIC; TAXA : IN STD_LOGIC_VECTOR(7 DOWNTO 0); PRESCALER : IN STD_LOGIC_VECTOR(7 DOWNTO 0); PWM : OUT STD_LOGIC ); end component; |

A tabela classifica as portas especificando suas funções:

| Nome da Porta | Tipo | Função |

| CLK | Entrada | Contém o valor do sinal de clock do componente. |

| RSTn | Entrada | Botão de reset negado. |

| HABILITA | Entrada | Ativa ou desativa o processo gera_prescaler. |

| INV_PWM | Entrada | Se ativo, inverte o PWM (não utilizado nesta aplicação). |

| HAB_SAIDAn | Entrada | Habilita a saída do sinal PWM (não utilizado nesta aplicação). |

| TAXA | Entrada | Razão cíclica. |

| PRESCALER | Entrada | Número inteiro maior ou igual a 0, que divide o sinal de clock de entrada se maior que zero. |

| PWM | Saída | Sinal PWM de saída. |

INSTANCIAÇÃO:

Entre o begin e o fim da architecture do arquivo de topo do projeto (rgb_teste.vhd) é necessário inserir a instanciação do componente:

*O código e a tabela mostra a instanciação para a cor vermelha apenas. A instanciação das outras duas cores é similar e pode ser vista na arquitetura de topo do projeto.

|

1 2 3 4 5 6 7 8 9 10 11 12 13 |

-- Instanciação do modulo de pwm para vermelho: VERMELHO_PWM_inst: modulo_pwm port map ( CLK => CLK_PWM, RSTn => RSTn, HABILITA => '1', INV_PWM => '0', HAB_SAIDAn => '0', TAXA => PWM_VERMELHO, PRESCALER => X"00", PWM => PWM_COR(2) ); |

A seguinte tabela classifica as portas, especificando a que sinal cada uma delas é atribuída:

| Nome da Porta | Atribuição | Justificação |

| CLK | CLK_IHM | Contém o valor do sinal de clock do componente. |

| RSTn | RSTn | Botão de reset negado. |

| HABILITA | ‘1’ | Ativa ou desativa o processo gera_prescaler. |

| INV_PWM | ‘0’ | Se ativo, inverte o PWM (não utilizado nesta aplicação). |

| HAB_SAIDAn | ‘0’ | Habilita a saída do sinal PWM (não utilizado nesta aplicação). |

| TAXA | PWM_VERMELHO | Razão cíclica. |

| PRESCALER | X”00″ | Número inteiro maior ou igual a 0, que divide o sinal de clock de entrada se maior que zero. |

| PWM | PWM_COR(2) | Sinal PWM de saída. |

Conclusão

O Controle de LED RGB com PWM é um exemplo simples de aplicação didática de PWM, e pode servir de referência para outros projetos. Ainda, é interessante exemplo da abordagem hierárquica do projeto, um conceito fundamental para o desenvolvimento de projetos avançados em sistemas digitais. A sua implementação no kit de CPLD MAXV do projeto FPGA para Todos é bastante facilitada pelos recursos já disponíveis na placa (LED RGB, botões, oscilador), e ocupa 189 elementos lógicos do CPLD. Os arquivos do projeto são disponibilizados para experimentação dos usuários.

Arquivos Disponíveis para Transferência

Nos arquivos abaixo, o projeto foi compilado para o componente 5M240ZT100C5 de 240 elementos lógicos. O kit de CPLD MAXV também é compatível com o componente 5M570ZT100C5 de 570 elementos lógicos. A adaptação deste projeto para outros componentes é bastante simples.

Projeto RGB_TEST: Projeto

Arquivo POF para gravação: Arquivo para Gravação