Unidade Lógica Aritmética

A Unidade Lógica Aritmética (ULA) é um bloco que executa operações aritméticas e lógicas. Entre as operações aritméticas que excuta, ela soma, subtrai, divide e determina se um número é positivo ou negativo ou se é zero. Ela pode também executar funções lógicas como “E”, “OU” ou “OU EXCLUSIVO”. A ULA é um bloco básico de um microprocessador ou CPU de um computador.

O projeto a seguir, é um exemplo de circuito lógico combinacional, descrito em VHDL e simulado no software ModelSim®-Altera, através do modo interativo.

Os módulos necessários para a implementação do projeto são:

- 1x Kit CPLD_7064;

- 1x Placa de LEDs;

- 2x Placas de Chaves.

Lógica de Funcionamento

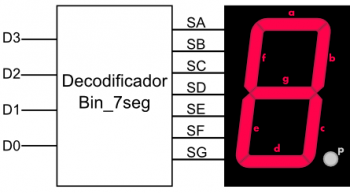

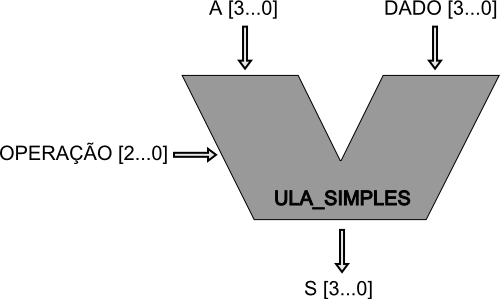

A ULA recebe duas palavras de 4 bits (A e DADO) e realiza uma operação entre as duas. A operação a ser efetuada é selecionada através da entrada OPERACAO conforme a tabela abaixo.

| OPERACAO | Operação realizada |

| 000 | Adição |

| 001 | Subtração |

| 010 | ‘E’ Lógico |

| 011 | ‘OU’ Lógico |

| 100 | ‘OU’ Exclusivo |

| 101 | Complemento do acumulador |

Para outras entradas, a ULA apresenta uma saída de alta impedância.

A Figura 1 apresenta o símbolo padrão para a ULA.

Figura 1 – Símbolo esquemático típico para a ULA

Este trecho de código descreve, em VHDL, a entidade ULA.

{code}

entity ULA_SIMPLES is

port

(

— Dados de Entrada:

A, DADO: in std_logic_vector (3 downto 0);

— Saída de Resultados (“Bruto”, sem flags)

S: out std_logic_vector (3 downto 0);

— Definição da operação a ser executada:

OPERACAO: in std_logic_vector (2 downto 0)

);

end entity ULA_SIMPLES;

{/code}

Este trecho de código apresenta o decodificador utilizado para selecionar a operação a partir da entrada OPERACAO. Utiliza-se a função case dentro de um processo.

{code}

— O código na entrada “OPERACAO”, de três bits, determina

— que tarefa a ULA simples executará.

case OPERACAO is

when “000” => S <= A + DADO; — Adição

when “001” => S <= A – DADO; — Subtração

when “010” => S <= A and DADO; — Lógica “E” bit a bit

when “011” => S <= A or DADO; — Lógica “OU” bit a bit

when “100” => S <= A xor DADO; — Lógica “OU EXCLUSIVO” bit a bit

when “101” => S <= NOT A; — Complemento do acumulador

when others => S <= “ZZZZ”; — Saída em alta impedância para operação indefinida…

end case;

{/code}

Uma vez selecionada, a operação é executada a partir das entradas A e DADO) ou apenas de uma que é o caso do NOT.

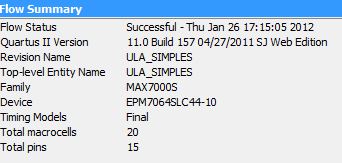

A Figura apresenta um resumo da Analise e síntese.

Figura 2 – Resumo do Resultado da Análise e Síntese.

Simulação

A Figura 4 apresenta as formas de onda da simulação. Foram adotados valores fixos para A e para DADO e para OPERACAO foi testado todas as possibilidades. Foi utilizado o ModelSim®-Altera de forma interativa (tutorial para a forma interativa, clique aqui).

Figura 3 – Formas de onda da simulação.

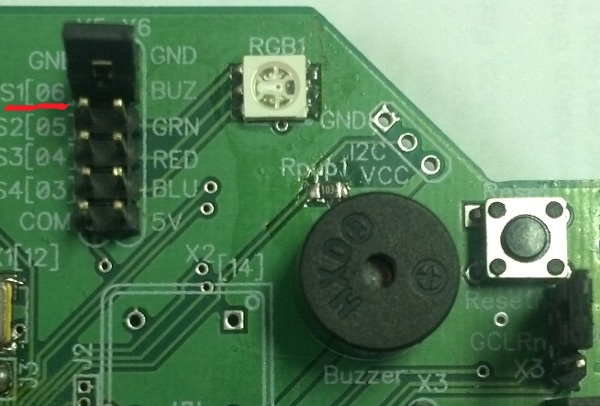

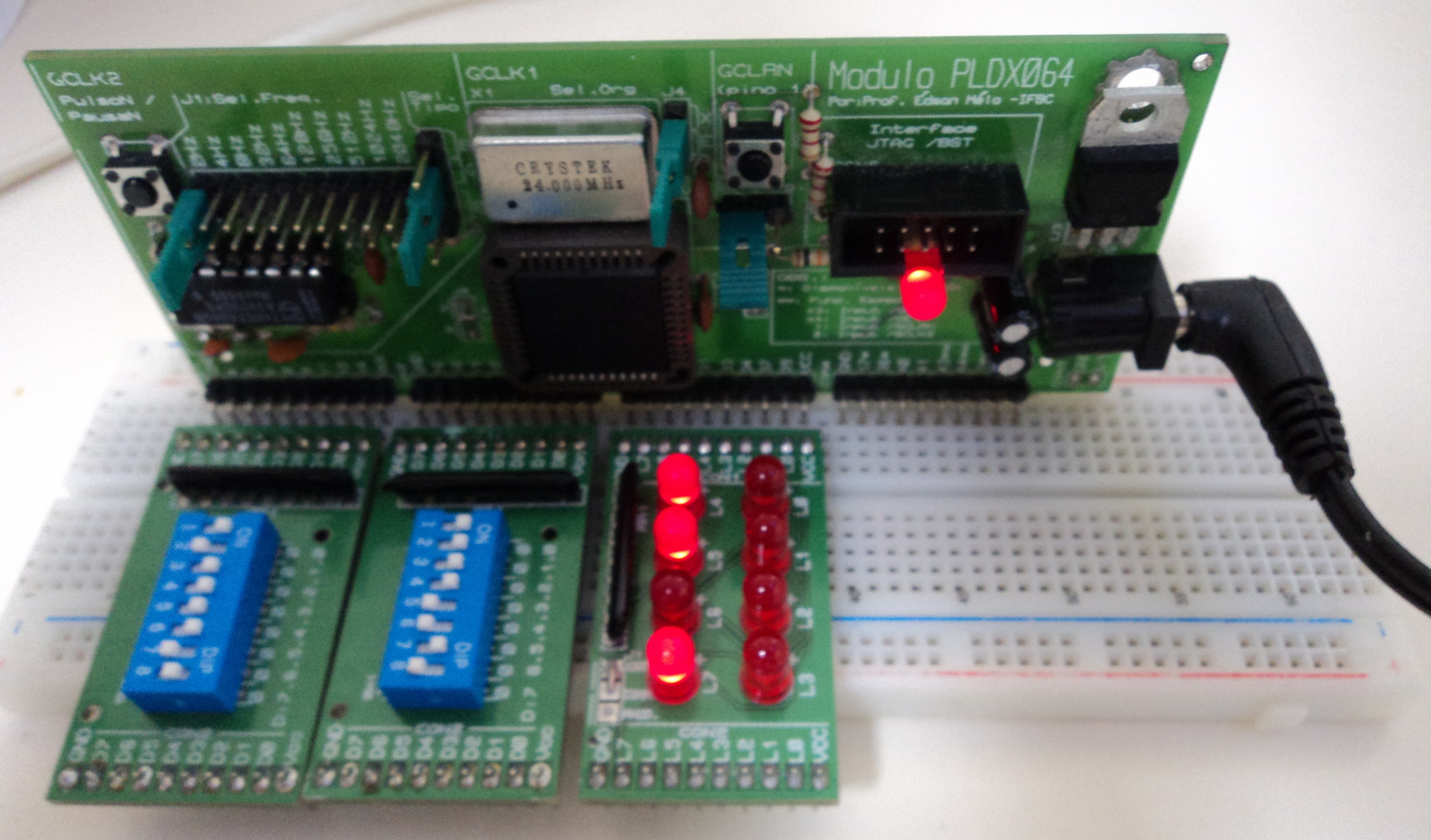

Estrutura Física

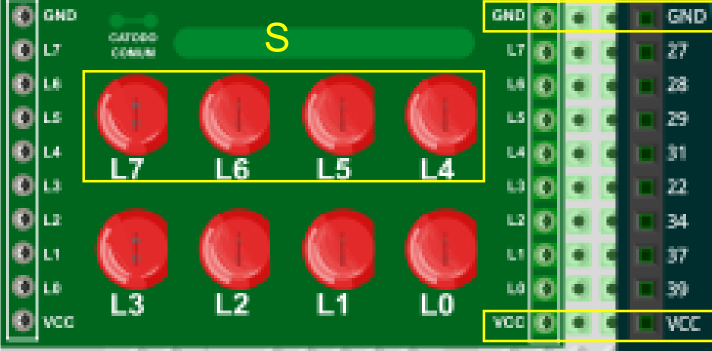

Para demonstrar o funcionamento da ULA, utilizamos chaves (para operandos e operação) e LEDs (para o resultado).

Na primeira placa de chaves, as 4 primeiras (7 a 4) são para a variável A e as 4 ultimas (3 a 0) para a variável DADO. Nos LEDs temos a apresentação do resultado.

Figura 4 – Estrutura Física do Projeto.

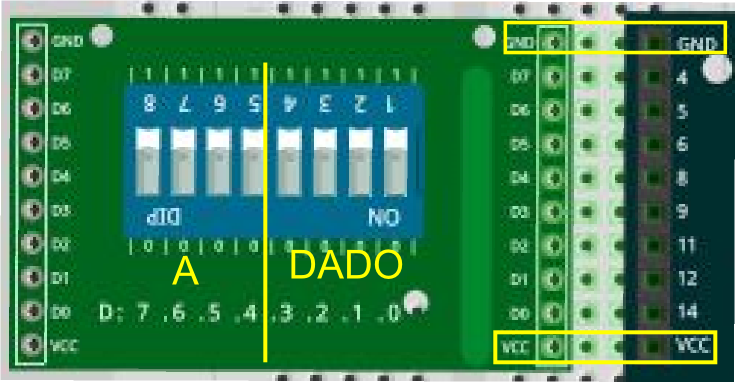

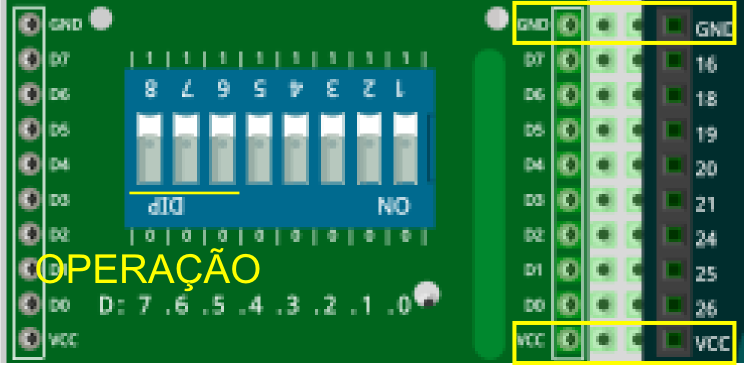

Montagem e Roteameno

As placas de chaves serão colocadas nos conectores CON1 e CON2 e a placa de LEDs será conectado no conector CON3, como mostrado nas ilutrações abaixo feitas no software Fritzing. Lembrando que deve-se ficar atento para que os pinos de Vcc e o GND dos periféricos fiquem alinhados entre as placas.

Figura 5 – Detalhe do CON1 na matriz de contatos.

Figura 6 – Detalhe do CON2 na matriz de contatos.

Figura 7 – Detalhe do CON3 na matriz de contatos

A Figura 8 apresenta o mapeamento dos pinos de acordo a disposição das placas acima apresentada.

Figura 8 – Pin Planner.

Arquivos do Projeto

Para o download do projeto completo, clique aqui.

O arquivo está no formato “zip”, e inclui, entre outros:

– O arquivo de projeto do Quartus “.qpf”

– A descrição no formato VHDL “.vhd”