Decodificador para Display de 7 Segmentos em VHDL Este artigo apresentará o desenvolvimento de um decodificador binário para display de 7 segmentos implementado em VHDL, que apresentará o valor hexadecimal no display. O projeto foi testado no ModelSim-Altera, através de um testbench. Figura 1: Bloco decodificador de 7 segmentos […]

CPLD

Contador de dois bits Este artigo mostra passo a passo a construção de um contador síncrono de dois bits utilizando flip-flops; o projeto trata-se de um exemplo de entrada em modo esquemático com o uso de componentes primitivos do Quartus II, e será convertido para VHDL e simulado no ModelSim-Altera. […]

Registrador Série-Paralelo (24 bits) O projeto a seguir pretende aumentar a disponibilidade de pinos de saída em projetos, problema muitas vezes encontrado, por meio de um Registrador Série-Paralelo. A ideia deste exemplo surgiu a partir de um artigo da Altera® publicado sobre “Implementing the Top Five Control-Path Applications with Low-Cost, […]

Recepção Serial – RS232 O projeto descrito nesse artigo tem como objetivo a implementação de um receptor serial com base no protocolo RS232, sendo um projeto complementar ao transmissor serial RS232, detalhado em outro artigo. Essa página demonstrará o exemplo de um projeto descrito em VHDL e simulado no Modelsim-Altera®, […]

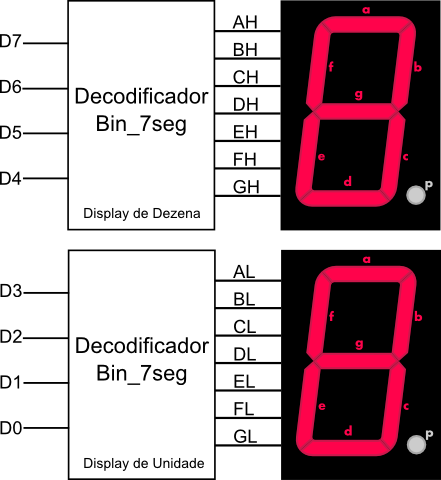

Decodificador Duplo para Display de Sete Segmentos Neste projeto, expandimos o circuito do decodificador de binário para 7 segmentos estudado no artigo “Decodificador para Display de Sete Segmentos” para a exibição de dois algarismos. Para diversos algarismos, pode ser interessante um processo de multiplexação, como mostrado no artigo “Multiplexação Display […]

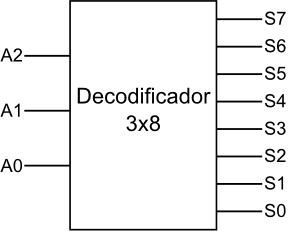

Decodificador 3×8 – Modo Esquemático O projeto pretende a partir de um código binário de três bits, selecionar uma das oito saídas, sendo a Figura 1 o bloco representativo do mesmo. Suas aplicações vão desde multiplexadores e demultiplexadores, até seleção de memória de entrada e saída (E/S). Figura 1: Bloco […]