Memoria RAM em FPGA Nesse artigo será apresentado um programa em VHDL utilizado para a escrita e leitura de uma memória RAM implementada dentro de um FPGA (CICLONE III), presente na placa de desenvolvimento DE0 . Para a implementação da memória utilizou-se a ferramenta de megafunções do QUARTUS© II. Devido […]

Monthly Archives: setembro de 2011

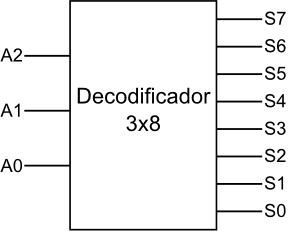

Decodificador 3×8 – Modo Esquemático O projeto pretende a partir de um código binário de três bits, selecionar uma das oito saídas, sendo a Figura 1 o bloco representativo do mesmo. Suas aplicações vão desde multiplexadores e demultiplexadores, até seleção de memória de entrada e saída (E/S). Figura 1: Bloco […]

Leitura Assíncrona de Teclado O projeto a seguir pretende fazer a leitura de um teclado matricial sem a utilização de clock. Basicamente, quando uma tecla é pressionada o circuito identifica qual a linha e coluna correspondente e decodifica a tecla. O presente artigo apresenta um exemplo de projeto feito em VHDL […]

Placa de Teclado Matricial Figura 1: Teclado Matricial Descrição do Circuito O teclado matricial é composto por 12 botões, distribuidos em 3 coluna e 4 linhas. Os botões, quando pressionados, conectam uma determinada linha a uma coluna, como será mostrado abaixo. As linhas e colunas são designadas por letras, em […]

Varredura de um teclado matricial O projeto apresentado abaixo tem o objetivo de ler um teclado matricial pelo processo de varredura, ou seja, testar linha por linha ou coluna por coluna para determinar a tecla pressionada. Neste projeto, como mostra a animação, são atribuídos valores as linhas de forma a […]