Contador de dois bits Este artigo mostra passo a passo a construção de um contador síncrono de dois bits utilizando flip-flops; o projeto trata-se de um exemplo de entrada em modo esquemático com o uso de componentes primitivos do Quartus II, e será convertido para VHDL e simulado no ModelSim-Altera. […]

Yearly Archives: 2011

Registrador Série-Paralelo (24 bits) O projeto a seguir pretende aumentar a disponibilidade de pinos de saída em projetos, problema muitas vezes encontrado, por meio de um Registrador Série-Paralelo. A ideia deste exemplo surgiu a partir de um artigo da Altera® publicado sobre “Implementing the Top Five Control-Path Applications with Low-Cost, […]

Recepção Serial – RS232 O projeto descrito nesse artigo tem como objetivo a implementação de um receptor serial com base no protocolo RS232, sendo um projeto complementar ao transmissor serial RS232, detalhado em outro artigo. Essa página demonstrará o exemplo de um projeto descrito em VHDL e simulado no Modelsim-Altera®, […]

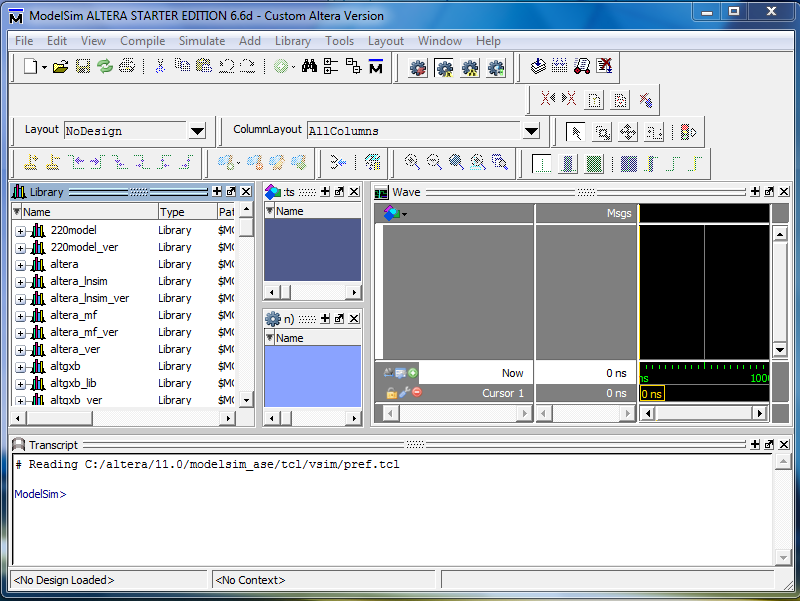

Simulação Interativa com o ModelSim-Altera Figura 1 – Abertura do ModelSim-Altera Para simulação de projetos feitos com o programa Quartus II, usamos o software ModelSim-Altera que é instalado juntamente com o Quartus II. Este software nos proporciona simulações em forma de onda, como ilustra a Figura 2, porém há duas […]

Microprocessador Descrito em VHDL Projeto enviado por: Pedro Augusto Ceriotti Graduando em Engenharia de Controle e Automação Universidade Federal de Santa Catarina Descrição do Projeto: Temos como objetivo final no desenvolvimento deste projeto a simulação da arquitetura de um microprocessador na linguagem de descrição de hardware VHDL, com um conjunto […]

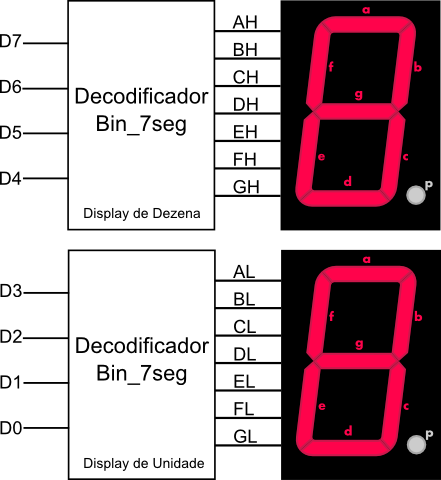

Decodificador Duplo para Display de Sete Segmentos Neste projeto, expandimos o circuito do decodificador de binário para 7 segmentos estudado no artigo “Decodificador para Display de Sete Segmentos” para a exibição de dois algarismos. Para diversos algarismos, pode ser interessante um processo de multiplexação, como mostrado no artigo “Multiplexação Display […]